Автоматический коммутатор фаз

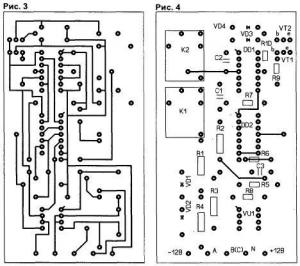

В народном хозяйстве широко применяется оборудование с питанием от трехфазной сети, требующее соблюдения порядка чередования фаз. Обычно это достигается соответствующей коммутацией проводов, но в ходе различных ремонтных работ, когда используются дополнительные питающие кабели либо временные распределительные щиты, при переключениях нередко возникает нарушение последовательности фаз, которое может вызвать выход из строя оборудования. Предлагаемое устройство (рис.1) обеспечивает правильный порядок чередования фаз на нагрузке при произвольном порядке ее соединения с трехфазной сетью.

Работает автоматический коммутатор фаз так. Отрицательная полуволна синусоидального напряжения фазы А проходит через диод VD1 и создает на нем падение напряжения около 0, 7 В. Светодиод оптрона VU1.1 не светится, так как к нему приложено обратное напряжение, фототранзистор оптрона закрыт. Положительная полуволна синусоидального напряжения фазы А проходит через светодиод оптрона VU1.1 изаставляет его светиться. Фототранзистор оп-трона VU1.1 открывается, и на его эмиттере (выводе 8) появляется высокий уровень напряжения. Ширина импульсов на эмиттере практически соответствует длительности полупериода входного сигнала.

Отрицательная полуволна фазы В (С) проходит через диод VD2. свето-диод оптрона VU1.2 не светится, и поэтому на выводе 5 — низкий уровень. При положительной полуволнеток протекает через светодиод VU1.2, транзистор этого оптрона открыт, и на выводе 5 VU1.2 — высокий уровень, который поступает на тактовые входы триггера DD2. Диоды VD1, VD2 необходимы, чтобы устранить высокое обратное напряжение на свето-диодах оптронов VU1.1 и VU1.2.

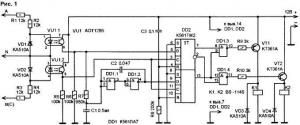

Выходной сигнал с оптрона VU1.1 подается на информационный вход верхнего триггера DD2 и на интегрирующую цепочку R7-C1. Тактовые импульсы устанавливают оба триггера в состояния, соответствующие уровням на их информационных входах в эти моменты времени. Изменения состояния триггеров происходят по фронтам тактовых импульсов (переходам 0 — 1 ). Таким образом, на прямом выходе (выводе 1) верхнего по схеме триггера DD2 — состояние "1" (высокий уровень), если резистор R3 подключен к фазе В, и "О* (низкий уровень), если он подключен к фазе С. Фаза, к которой подключен резистор R1, всегда принимается за фазу А. Такой информации достаточно, чтобы правильно подключить нагрузку к сети. Схема управления пускателями приведена на рис.2.

Сипчалы с прямого и инверсного выходов верхнего триггера поступают на входы логических элементов DD1.3 и DD1.4 (рис.1). Вторые входы этих элементов соединены с прямым выходом нижнего триггера DD2. Логический элемент DD1.1 вместе с интегрирующей цепочкой R7-C1 осуществляет задержку сигнала на время включения устройства. Элементы DD1.1, DD1.2 вместе с конденсатором С2 образуют триггер Шмитта, который вырабатывает сигналы с крутыми фрон-тами. Низкий уровень на выходе DD1.1 появляется в том случае, когда на его входах — "1". Это происходит тогда, когда напряжение на конденсаторе С1 превышает половину питающего. При указанных на схеме номиналах R7 и С1 '1" появляется на информационном входе D нижнего триггера DD2 приблизительно через 1 с после подачи напряжения на коммутатор. Выдержка необходима для предотвращения повтор но-кратковременных включений нагрузки, например, при ненадежных контактах или их искрении, что часто бывает при временных подключениях к сети. При кратковременном отключении сети оптрон VU1.1 не работает, на резисторах R5...R7 — "О", и конденсатор С1 быстро разряжается через резисторы R6, R7. Это приводит к появлению "О" на информационном входе (выводе 9) нижнего триггера DD2, который передается на выход триггера (вывод 13). Вследствие этого на выходах элементов DD1.3 и DD1.4 устанавливаются "1". транзисторы VT1. VT2 закрываются, и оба репе — К1 и К2 — отпускают. Следовательно, нагрузка обесточена.

С возобновлением подачи энергии выдержка времени повторяется. Цепочка R8-C3 устанавливает оба триггера в исходное состояние при включении питания. При нормальной работе коммутатора низкий уровень появляется только на одном выходе элементов DD1.3 или DD1.4. Одновременное появление низкого уровня на их выходах исключено, т.к. они управляются противофазными сигна-лами с верхнего триггера DD2.

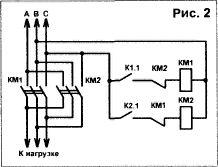

Устройство собрано на двухсторонней печатной плате, чертеж которой приведен на рис.3 и 4, а расположение элементов — также на рис.4.

Литература

1. А.Панкратьев. Автоматический коммутатор фаз. — Радио, 2007, №9, С.43.

В.КАЛАШНИК, Н.ЧЕРЕМИСИНОВА, г.Воронеж.